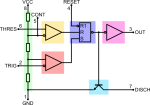

Fix in your mind that pins 3 and 7 are in phase, that is when 3 is high/low then 7 too.

But this depends by the S-R latch complementary output, which we called Q negated; if high/low then pins 3 and 7 become low/high.

We found a first step in solution; and keeping on going back we find again that all depends by the Set-Reset configuration in input, imposed with the correct values into pins 2 and 6.

So what now?

Simply the combinations (S,R) -> (1,0) or (0,1) (respectively Set and Reset) put Q negated low or high, resulting in pins 3 and 7 high or low; but pin 7 at low voltage means that the corresponding discharging BJT is electrically closed (Q negated is high) so that collector and emitter are nearly at the same voltage, that is zero because of emitter tied to ground.

But it's now clear that this offers a discharging path to the capacitor.

If we can distinguish the nature of this condition then automatically we know which state is stably kept by the monostable configuration.

Pin 2 - the trigger - is tied to Vcc through a resistor in a pull up form and is connected to ground but through a switch button which is open: because of this, pin 2 sees a voltage equal to Vcc (no current flowing through the resistor).

By closing the switch we tie the pin to ground, insuring it reaches a value less than 1/3 Vcc, making possible to have the Set for the latch.

So pin 7 is now high, in the sense that is pulled up by the resistor between it and Vcc, and the two resistors - fixed and variable - help the capacitor to charge.

We now can answer to the initial question about which of the two states a 555 maintains.

According to the initial scheme the low state is stable, because pin 2 is pulled-up; but nothing forbids us to invert the polarity, making the high state stable.

The difference relies upon the stability of the other state, so called quasi-stable: we'll describe it when talking about timing issues.

And we know why too: capacitor is initially discharged and pin 2 is high, so (S,R)=(0,0). Then by pressing the switch we get (S,R)=(1,0) and the capacitor is charged.

Finally, when pin 6 reaches 2/3 Vcc so giving an (S,R)=(1,1)... or not?

Couldn't it be (S,R)=(0,1) instead?

Next time we'll answer and we'll explain more about timing issues involved, also graphing the time response of 555 in monostable configuration and why the low state is the default stable one: plus discussing a variation to increase control on it.

Thank you!